Global Site

Displaying present location in the site.

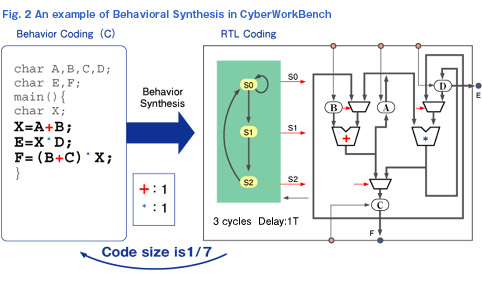

Behavioral Synthesis

"Behavioral Synthesis" plays a central role in CyberWorkBench®. The behavioral synthesizer generates the RTL circuit from a behavioral specification. It quickly synthesizes algorithms written in C, such as for encryption or image processing, into an RTL circuit that meets the design requirements in terms of clock speed, chip area, power consumption, etc.

The main features of the behavioral synthesizer are as follows:

-

high-speed and high-precision synthesis

-

extensive synthesis options that enable designers to explore a wide range of circuit architectures (area/performance trade-offs).

-

various tuning knobs that support design requirements such as multiple clocks, gated clocks, synchronous/asynchronous reset, and synchronous/asynchronous/pipeline memory.

Figure 2 illustrates an example of behavioral synthesis, and Fig. 3 shows the GUI of CyberWorkBench. All work involving LSI design is done in C. Testing and debugging can be done with the C source code, and the formal property checker can verify properties described in C. RTL debugging is not necessary in CyberWorkBench®.

Click to Enlarge

Click to Enlarge CyberWorkBench Brochure

CyberWorkBench Brochure