Global Site

Breadcrumb navigation

ESD和PI选项

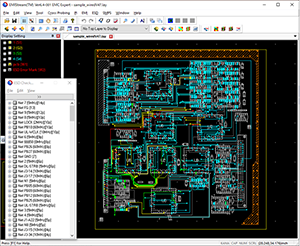

防静电规则检查和电源完整性分析(PIStream)也是EMIStream的选项

ESD规则检查

带电人体等接触电子设备时会产生激烈的放电。这种现象被称为ESD (Electrostatic Discharge: 静电放电) ,它是电子设备发生误动作和受到损伤的原因。

EMIStream ESD 检查功能可以找出电路板设计中的耐ESD性低的部位,并对此提出改进建议。

- 采用根据国内外企业的经验,经NEC研究所验证的有效检查项目及阈值。

- 设计的初期阶段就可采取ESD对策,减少了后期样机评估后的整改时间。

- 读入CAD数据后经简单设定就可进行检查。

- 可在短时间内确定有ESD问题的地方,便于迅速采取对策。

10项规则检查

ESD检查由信号布线检查群、对策元件布局妥当性检查群、FG结构检查群等10个检查项目构成。

信号布线检查群

- 接近平面边缘的布线(Traces Near Plane Edge)

- 走线穿越电源和接地平面(Traces crossing over power and ground plane)

- 跨越缝隙布线(Signal trace over the slit of the ground/power plane)(* 1)

- SG模式布线(SG Trace)

- SG布线过孔间距(SG Via Spacing)

- 电源端保护(Power Protection)

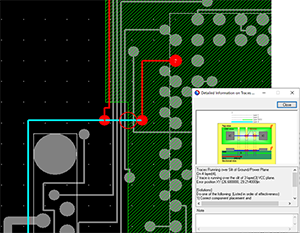

(* 1)跨越缝隙布线

信号线在地平面和电源平面的缝隙或孔上通过的话,信号上会被叠加上较大的ESD干扰。本检查可以查出这种结构并显示出错警告。

对策元件布局妥当性检查群

- I输入端脚保护(Input Pin Protection)

- 电源端脚保护(Power Pin Protection)

- 复位线保护(Reset Line Protection)(*2)

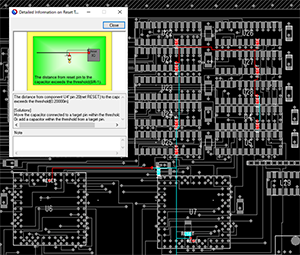

(*2)复位线保护

为了解决ESD问题,可以对耐ESD干扰性低的信号线和电源采用对策元件(电容等),但是如果放置的位置不对则会降低对干扰的抑制效果。本检查功能可以检查对策元件的放置位置,当放置位置不当时会显示出错警告。

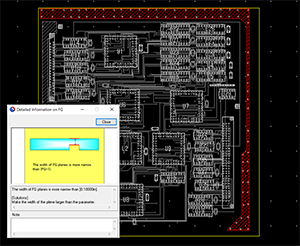

FG结构检查群

FG Pattern

对于ESD电流排放路的FG结构形式,线宽和层间过孔间位置不对的话,干扰会围绕在信号线和电源层地层里。另外,从FG结构到电源层或接地层的距离也与噪音的环绕有很大关系。本检查能检查出FG结构、并检查与电源层地层的距离。如果有问题,会显示警告信息。

电源完整性分析

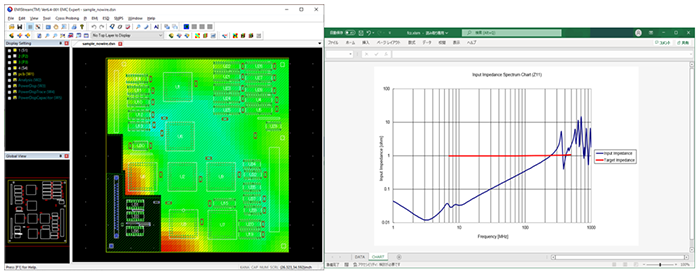

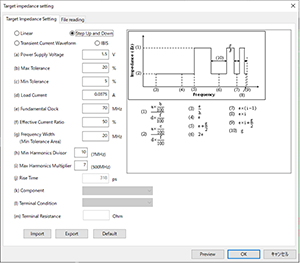

电源完整性分析功能可以兼顾EMI和PI双方来进行设计。可以分析从IC位置到PCB的电源平面与接地平面间的阻抗(输入阻抗),并与阈值的目标阻抗进行比较。

通过使用此功能,可以通过为防止IC误动作而放置或移动电容器、改变电容值、改变平面形状以及电源与接地平面的距离等措施来达到输入阻抗满足目标阻抗的目的。

PIStream也可以单独使用。

IC模型生成用GUI

可以很容易地输入对PI有重要意义的、影响MID-Frequency Resonance的IC芯片的容值以及IC芯片封装常数。因此可以更正确地决定电路板上应放置的电容。

Contact