# **Development of EFLIP, A Lithium-Ion Battery Protection MOSFET**

FUKUCHI Kazuhiro, HIRAMATSU Shinichi, YAMADA Yukiko, Tai Siew CHIN, FUJIE Kouji, KUBOGATA Masayuki

#### Abstract

NEC Electronics has been marketing MOSFET products for protecting the lithium-ion batteries used in cellular phones.

The newly developed CSP-type MOSFET, named the EFLIP, is a lithium-ion protection MOSFET of the smallest class, with a package mounting area of only 2.6mm<sup>2</sup>. It is expected to contribute significantly to a reduction in lithium-ion battery packs and the mobile equipment that incorporates them.

#### Keywords

lithium-ion battery, MOSFET, CSP

### **1. Introduction**

The lithium-ion battery is used in cellular phones, PDAs and mobile audio equipment that are presently achieving rapid growth.

The lithium-ion battery originally has a compact size and large capacity. However, as it could be damaged by overcharging or discharging, a discrete (mold packaged) MOSFET is usually used as the device for protecting the battery.

As the current trend in size and thickness reduction of mobile equipment has promoted a need for size and thickness reduction of lithium-ion battery packs, the protection circuit MOS-FET is also being subjected to the need for size reduction.

NEC Electronics has recently developed a CSP MOSFET specialized for the lithium-ion battery protection of the smallest class, and called it the EFLIP (Ecologically Flip chip MOS-FET for Lithium-Ion battery Protection).

### 2. Market Requirements for Lithium-Ion Battery Protection Circuitry and Protection MOSFET

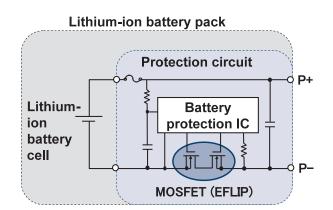

**Fig. 1** shows the basic configuration of a lithium-ion battery pack.

The lithium-ion battery pack is composed of the protection circuitry including the recharge/discharge control IC that monitors and controls overcharge and over-discharge and the MOSFET that shuts off the circuitry in case of abnormality, in addition to the lithium-ion battery cell.

Since such mobile devices are always carried on the person, various accidents are often encountered, which for example include the shorting of the lithium-ion battery terminals. If the

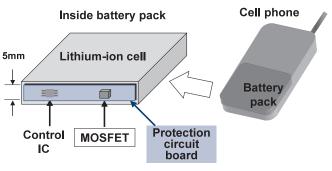

Fig. 2 Image of internal structure of lithium-ion battery.

battery output is not shut down immediately in such a case, the continued current flow may cause burns or fire due to the heat. This is the reason that the protection circuitry requires a MOS-FET that functions as a switch.

Fig. 2 shows the image of a lithium-ion battery pack and its protection circuit board.

The protection MOSFET should be of a compact size because it is in general mounted on a substrate with a width of less than 5mm that is located on the side of the thin lithium-ion battery cell. Consequently, reduction in the battery cell size makes it necessary to reduce the size and thickness of the MOSFET.

# 3. Features of EFLIP, Lithium-Ion Battery Protection MOSFET

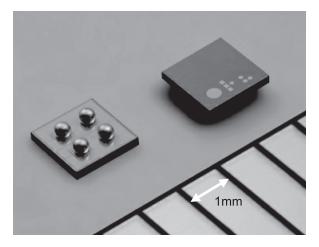

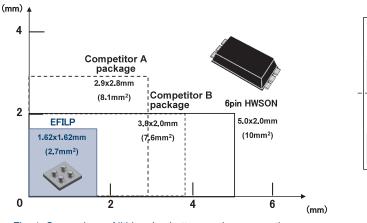

**Fig. 3** shows a photo of the recently developed EFLIP and **Fig. 4** shows the comparison of the mounting area between the new EFLIP and our previous mold package.

Fig. 3 External view of the EFLIP.

To meet the market needs for more compact and thinner packages, the EFLIP has been implemented with a mounting area of about 1/4 (2.6mm<sup>2</sup>) of our previous 6-pin HWSON mold package and the very low package height of 0.55mm.

With a mounting area ratio of less than 50% compared to the packages from competitors (A and B), the EFLIP can be regarded as the lithium-ion battery protection MOSFET of the smallest class that is obtainable worldwide.

Now let us see the technology that allows the EFLIP to reduce the mounting area significantly compared to the previous products.

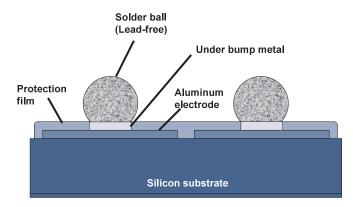

**Fig. 5** shows the cross-sectional structure of the EFLIP, and **Fig. 6** shows its bottom view and operation (On current flow direction).

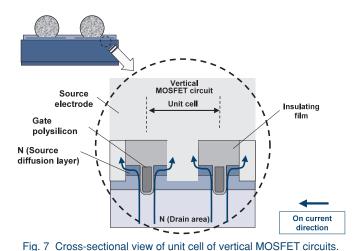

The EFLIP is composed of two vertical MOSFET circuits formed on a silicon substrate, and two solder balls are formed on each MOSFET circuit for use as its gate and source

Backside metal Fig. 5 Cross-sectional structure of EFLIP.

Fig. 4 Comparison of lithium-ion battery package mounting area.

A' MOSEET2 MOSFET1 MOSFET2 Gate 2 Source 2 Sour Source electrode Drain area Gate 1 Source 1 Drain electrode On current direction Α Cross-sectional view of EFLIP Bottom view of EFLIP (Line A-A')

Fig. 6 Bottom and cross-sectional views of EFLIP products.

## **Development of EFLIP, A Lithium-Ion Battery Protection MOSFET**

electrodes.

The lithium-ion battery protection MOSFET product is composed of "a series of two circuits" and uses a "common drain" as shown in Section 2 (Fig. 1), and we have implemented the drain layers of the two MOSFET circuits with one silicon substrate and fabricated only the gate and source terminals (solder balls) as the electrodes for the two MOSFET circuits on the protection circuit board. This was one of the factors that has made it possible to provide the device with such a size reduction feature.

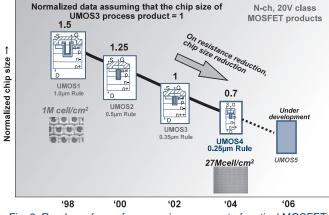

For the fabrication of the vertical MOSFET circuits formed on the silicon substrate as shown in **Fig. 7**, we adopted the UMOS4 process for the EFLIP, which is the latest diffusion process for vertical MOSFET circuits. We thus succeeded in reducing the chip size for achieving the same ON resistance performance as before by about 30% compared to the previous

Fig. 8 Roadmap for performance improvement of vertical MOSFET circuits process.

UMOS3 process. This was another factor that enabled the size reduction (see **Fig. 8** that shows the trends of performance improvement of the vertical MOSFET circuit fabrication processes).

The recently developed EFLIP has been subjected to NEC Electronics in-house strength testing (bending test under the board mounting condition, dropping test, etc.) and reliability testing (temperature cycle test, etc.) assuming the application to the protection circuit board in lithium-ion battery packs. It has proved to have almost equivalent strength and reliability to the previous mold package products.

#### 4. Characteristics and Lineup of Products

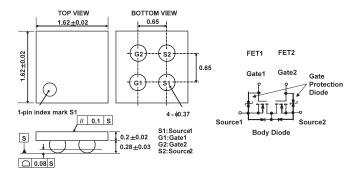

**Fig. 9** shows the external dimensions and internal equivalent circuitry of the EFLIP package, and **Table** shows the product lineup and main characteristics.

We prepared two kinds of products with the rated sourcesource voltages of 20V and 30V respectively to allow their use by a wider range of users.

#### **5.** Conclusion

The EFLIP, the recently developed MOSFET for use with lithium-ion batteries protection, is of the smallest class available worldwide and thus contributes significantly to the size and thickness reduction of lithium-ion battery packs.

At NEC Electronics, it is our intention to continue the development of even more compact and higher performance MOS-FET devices for lithium-ion batteries by our efforts to reduce the package size and by developing the most advanced wafer processes.

Fig. 9 Dimensions and equivalent internal circuitry of EFLIP product.

#### Table EFLIP product characteristics and lineup.

| I                     | tem Name           |           | μPA2350 | μPA2351 | Unit |  |

|-----------------------|--------------------|-----------|---------|---------|------|--|

| Item                  | Symbol             | Condition | Rating  | Rating  | Unit |  |

| Source-source voltage | V <sub>SSS</sub>   | VGS=0V    | 20      | 30      | V    |  |

| Gate-source voltage   | V <sub>GSS</sub>   | VSS=0V    | ±12     | ±12     | V    |  |

| Source current        | I <sub>S(DC)</sub> | -         | 6       | 6       | А    |  |

| Channel temperature   | Tch                | -         | 150     | 150     | °C   |  |

### Absolute maximum rating (Ta = $25^{\circ}$ C)

#### Electrical characteristics (Ta = $25^{\circ}$ C) Common for FET1 and FET2.

| Item Name                      |                      |                | μPA2350 |     |     | μPA2351 |     |     | Unit |

|--------------------------------|----------------------|----------------|---------|-----|-----|---------|-----|-----|------|

| Item                           | Symbol               | Condition      | MIN     | TYP | MAX | MIN     | TYP | MAX | Unit |

| Source cutoff current          | I <sub>SSS</sub>     | VSS=VSSS       |         |     | 1   |         |     | 1   | μΑ   |

| Gate cutoff current            | I <sub>GSS</sub>     | VGS=±12V       |         |     | ±10 |         |     | ±10 | μΑ   |

| Source-source<br>on resistance | R <sub>SS(on)1</sub> | VGS=4.5V,IS=3A | 22      | 28  | 35  | 24      | 32  | 40  | mΩ   |

|                                | R <sub>SS(on)2</sub> | VGS=4.0V,IS=3A | 23      | 29  | 37  | 25      | 33  | 42  |      |

|                                | R <sub>SS(on)3</sub> | VGS=3.1V,IS=3A | 24      | 33  | 44  | 28      | 37  | 50  |      |

|                                | R <sub>SS(on)4</sub> | VGS=2.5V,IS=3A | 30      | 41  | 55  | 31      | 45  | 64  |      |

## **Authors' Profiles**

FUKUCHI Kazuhiro Senior Design Engineer, Power Management Devices Division, 5th Systems Operations Unit, NEC Electronics Corporation

HIRAMATSU Shinichi Team Manager, Power Management Devices Division, 5th Systems Operations Unit, NEC Electronics Corporation

YAMADA Yukiko Staff, Power Management Devices Division, 5th Systems Operations Unit, NEC Electronics Corporation

Tai Siew CHIN Associate Specialist, Manufacturing Engineering Department, NEC Semiconductors Malaysia

FUJIE Kouji Assistant Manager, Power Management Devices Division, 5th Systems Operations Unit, NEC Electronics Corporation

KUBOGATA Masayuki Assistant Manager, Power Management Devices Division, 5th Systems Operations Unit, NEC Electronics Corporation