# CYBERWORKBENCH

NEC's High Level Synthesis Solution

SEPTEMBER 01, 2016 NEC INDIA PVT LTD [Company address]

# Contents

| Introduction                                                                 | 2  |

|------------------------------------------------------------------------------|----|

| C-Based Design Flow                                                          | 3  |

| Basic Concept of CyberWorkBench                                              | 3  |

| Design Tool Overview                                                         | 3  |

| Synthesis Flow                                                               | 4  |

| Verification Flow                                                            | 5  |

| Behavioral Synthesis                                                         | 6  |

| Behavioral Synthesis Advantages over Conventional Flows                      | 8  |

| Shorter Design Period and Less Design Cost                                   | 8  |

| Source Code Reusability and Behavioral IPs                                   | 9  |

| Configurable Processor Synthesis                                             | 10 |

| Automatic Architecture Exploration                                           | 10 |

| System VLSI Design Example Using C-Based Behavioral Synthesis                | 11 |

| Summary and Conclusion                                                       | 12 |

| Detailed Specification of CWB                                                | 13 |

| Behavioral Synthesis                                                         | 13 |

| Input supported                                                              | 13 |

| Output Languages                                                             | 15 |

| Target Device Supported                                                      | 16 |

| Input Constraints                                                            | 17 |

| Behavioral Synthesis modes or Scheduling options (C to RTL conversion modes) | 19 |

| Other Features                                                               | 19 |

| Verification                                                                 | 33 |

| Integration with Third Party Tools                                           | 37 |

#### Introduction

The design productivity gap problem is becoming more and more serious as VLSI systems become larger. In the mid-1980s, gate-level design shifted to register transfer level (RTL) design for designs that typically exceeded 100K gates.

Currently, several million gates circuits are commonly used just for random logic parts of a design, which equate to more than several hundred thousand lines of RTL code. It is therefore needed to move the design abstraction one more level in order to cope with this increasing complexity. Behavioral synthesis is a logical way to go as it allows "less detailed design description" and "higher reusability".

A higher level of abstraction description requires smaller code and provides faster simulation time. For example a one million gates circuit requires about 300K lines of RTL (Verilog or VHDL) code, but only around 40K lines of C code. The RTL simulation of 300K lines, is on an average takes 10 to 100 times than the 40K lines of equivalent behavioral code.

The benefits of behavioral synthesis are palpable through multiple commercial chip successes, thus Behavior Synthesis, or High Level Synthesis, is gaining acceptance within the design community. Various commercial chips for printers, mobile phones, set-top boxes and digital cameras are being designed using behavioral synthesis these days. ANSI-C is the preferred programming language for behavioral synthesis because embedded software is often described in C and design tools like compilers, debuggers, libraries and editors are easily available and there is a big amount of legacy code.

Presenting here an overview of C-based design flow where the efficiency and simulation performance is compared against pure RTL with co-simulating it with embedded software. C-based behavioral IPs are advantageous over RTL IPs and the application specific processors can be benefited from it. The hardware architecture explorer at the behavioral level allowing a fast and easy way to study the area, performance and power trade-offs of different designs automatically.

This document covers how behavioral synthesis can be used for any hardware module (data and control intensive).

# C-Based Design Flow

NEC have been developing C-based behavioral synthesis called "Cyber" since the late 80's and developing C-based verification tools such as formal verification and simulation around Cyber during the last 20 years All these tools are integrated into an IDE, where designers execute these tools upon the C-source code. The name of this IDE tool suite "CyberWorkBench"(CWB).

# Basic Concept of CyberWorkBench

The main idea behind CyberWorkBench is an "all-in-C" approach. This is built around two principal ideas:

- "All-in-C Synthesis": means that all modules in a VLSI design, including control intensive circuits and data dominant circuits, should be described in behavioral C language. The system supports legacy RTL or gate net list blocks as black boxes, which are called as C functions. At the same time it allows designers to create all new parts in C.

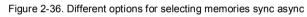

- 2. "All-in-C Verification": means that Verification (including debugging) tasks should be done at the C source code. In behavioral synthesis, a designer should not have to debug the generated RTL code. The CWB environment allows a designer to debug the original C source code and the CWB model checker allows designer to write properties or assertions directly on the C source code.

# **Design Tool Overview**

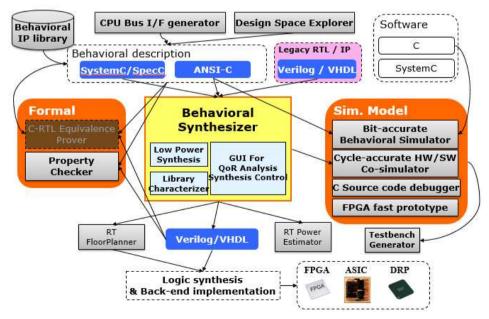

CWB targets general LSI systems which normally contain several CPUs or DSPs, dedicated hardware modules and some pre-designed or fixed RTL-or gate level IP modules, which are directly connected or through buses.

Initially, each dedicated hardware module is described in behavioral C. Once its functionality is verified using the C simulator and debugger, the hardware module is synthesized with the behavioral synthesizer. Configurable processors are also synthesized from the C description in CWB environment. Legend RTL modules are described as function, and handled as a black box.

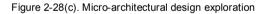

The CPU bus and bus interface circuits are automatically generated using a CPU bus library. After synthesizing and verifying each hardware module, the design environment allows designers to create a cycles-accurate simulation model for the entire system including CPUs, DSPs and custom hardware modules. With this simulation model, designers can verify both functionality and performance of their hardware design as well as the embedded software run on the CPU, DSP and/or generated configurable processors. The behavioral C source code can also be debugged with the formal verification, property/assertion model checker tool. Global properties and in-context (immediate) assertions are described for/in the C source code. The equivalence between behavioral C and generated RTL can be verified both in dynamic and static way.

#### Synthesis Flow

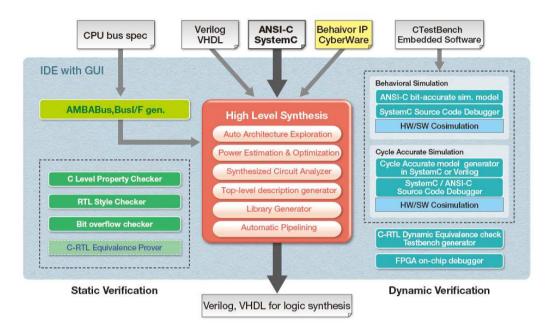

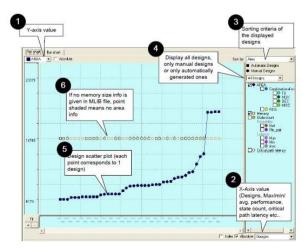

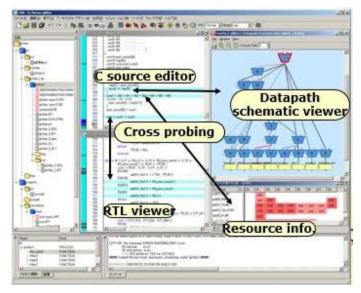

The CWB design flow is shown in Figure 1-1. A hardware design in extended ANSI-C (called "BDL", or "Cyber-C"), or SystemC is synthesized into synthesizable RTL with the "Cyber" behavioral synthesizer with a set of design constraints such as clock frequencies, number and kind of functional units and memories. Usually RTL is handles as a black box, but if necessary, the RTL can also be fed to behavioral synthesis. The behavioral synthesizer can insert extra registers to speed up the original RTL and generate new RTL of smaller delay. It also generates a cycle accurate simulation models in C++ or SystemC. The behavioral synthesis can therefore be considered as a Verilog, VHDL, C, C++, and SystemC unification step.

Fig 1-1. CyberWorkBench<sup>TM</sup> design flow

The "RTL Floor Planner" takes the RTL modules generated by the behavioral synthesizer with estimated area. Accurate timing information is extracted from the floor planner and fed back to the behavioral synthesizer. The behavioral synthesizer reads the timing information and reschedules the C code considering this.

#### Verification Flow

The functionality of the hardware described in C can be verified at the behavioral level, while performance and timing are verified at the cycle-accurate level (or RTL) through simulation. CWB has a behavioral C source code debugger linked to the cycle-accurate simulation and FPGA emulation tool. After verifying each hardware module, the entire SoC is simulated in order to analyze the performance and/or to find inter-modules problems such as low performance through bus collision, or inconsistent bit orders between modules. Since such entire chip performance simulation is extremely slow in RTL-based HW-SW co-simulation. CWB generates cycle accurate C++ simulation models which can run up to hundred times faster than RTL model. The HW-SW co-simulator, uses the generated cycle-accurate model for this purpose. The simulator allows designers to simulate and debug both hardware and software at the C source code level at the same time. If any performance problems are found, designers can change the hardware-software partitioning or algorithm directly at the C level, and can then repeat the entire chip simulation. This flow implies a much smaller and therefore faster redesign cycle than in a conventional RTL methodology. This entire chip simulation can be further accelerated using an FPGA emulation board. A "Testbench Generator" helps designers to run an RTL simulation with test patterns for behavioral C simulation faster and easier. Its inputs are test patterns for the C simulation and outputs a Verilog and/or VHDL testbench, which generates stimulus for the RTL simulation. It also creates a script to run commercial simulators to feed the behavioral test patterns and check the equivalence of outputs patterns between the behavioral and RTL simulation.

Another important feature of CWB is the formal verification tools, which is tightly linked to the behavioral synthesizer. With the behavioral synthesis information the formal verification tools can handle larger circuits than usual RTL tools and have C-source level debugging capability even though the model checker works on the generated RTL model. "C-RTL equivalence prover" checks the functional equivalence between a behavioral (un-timed or timed) C description and the generated RTL, using information on of the optimizations performed such as

loop unrolling, loop merge and array expansion performed by the behavioral synthesis. Without such information, the equivalence check is almost impossible for a large circuit.

Designers can specify assertions or properties at the behavioral C level, similar to the cycle accurate simulator. Such behavioral level properties/assertions are converted into RTL ones automatically, and are passed to our RTL model checker.

CWB generates a power enhanced RTL model which estimates the power consumed by the design. A set of power libraries for different technology is provided and used with the generated RTL estimates that power for the selected technology.

A "QoR" synthesis report file of the generated circuit shows a quick overview of the design quality. The report file includes area, number of states, critical path delay, number of wires and routability. This information is used for quick micro-architectural exploration as well as system architectural exploration. The system architecture explorer automatically generates different hardware architectures based on the preferences and constraints entered by the user (area, latency, power) at the C level. The designer can analyze the different generated architectures and finally choose the one that meets the design constraints at the smallest cost.

# **Behavioral Synthesis**

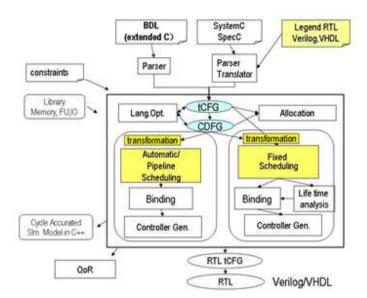

To support the "all-in-C" paradigm presented before, the behavioral synthesizer must cope with three types of circuits: (i) data-dominated, (ii) control-dominated, and (iii) control-flow intensive (CFI) ones. The three types of synthesis engines in order to support these varieties of circuit types: (i) automatic scheduling for CFI and data-flow circuits, (ii) fixed scheduling for control-dominated circuits, and (iii) pipeline scheduling for automatic pipelining or loop folding. Figure 1-2 shows a block diagram of CWB's synthesizer engines.

Control dominated circuits such as PCI I/F, DMA controller, DRAM controller, Bus Bridge, etc., require cycle-by-cycle behavior description, which is fit for timing chart. The extended C language BDL can describe clock boundary in a behavioral description, and is able to express very complex timing behavior concisely. Such description is synthesized with "fixed scheduling" engine. For that circuits, which require fixed sequential communication protocols but all other computations can be freely scheduled, automatic scheduling engine is used for synthesis.

Fig 1-2. Configuration of Cyber Behavior Synthesis

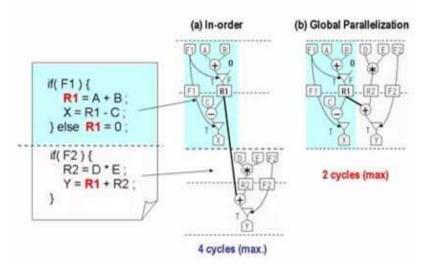

For CFI circuit synthesis, scheduling and allocation techniques play a major role. The quality of synthesis is affected by the control flow structure. A smart scheduling algorithm must be designed to overcome the effects of the programming style. The scheduler will have to modify the control logic in order to obtain circuits with less latency while maintaining the data-flow intact.

Merging two branches into a single using CDFG transformation is not as effective because the procedure is complex and the merging does not always lead to better results. Thus, this approach uses a systematic scheduling algorithm without CDFG transformations. In other words, the scheduler schedules all operations in several basic blocks and several branches at the same time in a unique way, as if they were all operations in a single basic block. The approach handles many other types of speculations, global parallelization with a method called "Generalized Condition Vector", which is extended version of "Condition Vector"

Fig 1-3. Parallelization of multiple branches for control-flow intensive applications (CFI)

### Behavioral Synthesis Advantages over Conventional Flows

The next subsections describes in detail some of the advantages of behavioral synthesis over conventional RTL methodologies like hardware-software co-design, source code re-usability, application specific processor optimizations and automatic architecture exploration.

#### Shorter Design Period and Less Design Cost

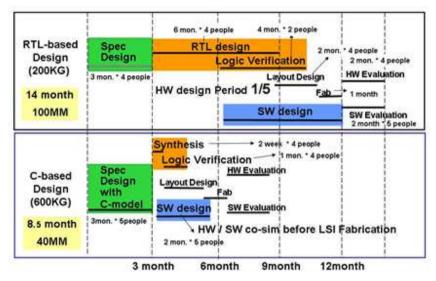

Since C-based behavioral synthesis automates the functional design of hardware, it shortens the design cycle and at the same time shortens the design time of embedded software. Figure 1-4 shows the design cycle of two designs. The first uses the traditional RTL-based design flow and the second the proposed C-based design flow. The total design period and design menmonth for the RTL-based design is larger than the C-based one, even though the gate size for RTL design (200K) is one third of that for the C-based (600K) one. The hardware design period of the C-based design is 1.5 months, much shorter than the RTL-based design takes 7 months. It needs to be stressed that the software design in the C-based design takes only 2 months while it takes 6 months for the RTL-based. This is due to the fact that the embedded software can be debugged before the IC fabrication using the hardware-software co-simulator. In RTL design, the software is usually verified on the evaluation board since RTL co-simulation is too slow even for this size of circuits. Lastly, C-based design allows very quick generation of simulation models for embedded software at a very early stage, allowing hardware and software to be concurrently designed both in C.

Fig 1-4. Comparison of Design Periods with C-based and RTL- based Design

#### Source Code Reusability and Behavioral IPs

Another important aspect of CWB is the high-reusability of behavioral models, we call this as "behavioral IP" or "Cyberware". An RT level reusable module, called "RTL-IP", can be successfully used for circuits of fixed performance such as bus interface circuits. However, RTL-IPs for general functional circuits such as encryption can only use for a specific technology, since the RTL-IP's "performance" is hard to adapt for newer technologies. On the contrary, a behavioral IP is more flexible and more reusable than RTL-IPs, since it can change its structure and behavior allowing the synthesis tool can generate circuits of different performances by simply changing high level synthesis constraints such as number of functional units and clock frequencies. Table-1-1 shows how various circuits of different "clock-frequency" can be generated from a single behavioral IP. This IP is a BS broadcast descramblers (Multi2). All generated circuits satisfy the required performance (more than 80Mbps) at various frequencies. Note that the highest clock circuit (108 MHz) uses less number of gates than the slow circuit (33MHz). This never happens in RTL-IPs, which follow the area-delay tradeoff relation of logic synthesis. A behavioral synthesizer generates a smaller circuit of higher clock frequency for the same performance, since less parallel operations are necessary to achieve the same performance at higher clock frequency.

| Clock Frequency | Generated<br>Gate size | Generated<br>RTL size | Performance |

|-----------------|------------------------|-----------------------|-------------|

| 33MHz           | 57KG                   | 7.0KL                 | 80Mbps      |

| 54MHz           | 42KG                   | 5.9KL                 | 80Mbps      |

| 108MHz          | 26KG                   | 2.5KL                 | 80Mbps      |

Table 1-1. BS broadcast descrambler behavioral IP comparison

Another important aspect is behavioral IPs are much easier to modify their "functionality" and "interface" than in RTL-IPs.

The behavioral IPs sometimes generates smaller circuits than RTL IPs as behavioral synthesis share registers and functional units for sequential algorithms, but recent RTL designers do not usually share registers since such time multiplexed sharing makes RTL simulation and debug very difficult.

#### Configurable Processor Synthesis

Since chip fabrication cost have raised considerably, SoC are becoming as flexible as possible. For this purpose, recent SoC usually have several configurable processors besides a main CPU. These configurable processors should be small, have a high performance and low power consumption for a specific application. Such a configurable processor is also called Application Specific Instruction set Processor (ASIP). ASIPs employ custom instruction-sets to accelerate some applications. The CWB provides ASIP's base processor and supplementary instructions that are described fully in behavioral C, which are behavioral synthesized. This allows the baseprocessors and the addition of instructions to share functional units. This sharing leads to much smaller circuits than the conventional RTL-based ASIPs. C-based ASIPs are more flexible than RTL-based ones in terms of public register number, pipeline stages or interrupt policy.

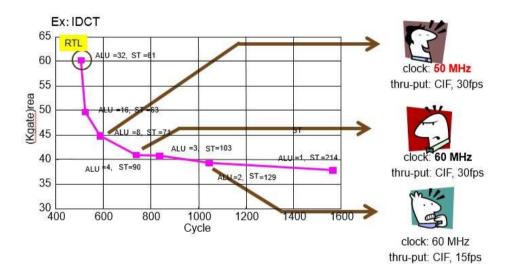

#### Automatic Architecture Exploration

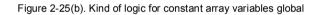

CWB allows the creation of multitude hardware architecture for a unique C design. The user can specify a set of constraints which all architectures have to meet (e.g. area, latency, power) and a set of different architectures that meets those constraints will automatically be generated. The area-performance-power trade- offs can be easily analyzed and the architecture that meets the constraints with the lowest cost can be chosen by the designer.

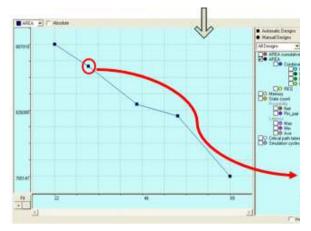

Fig 1-5. Automatic Architectures Exploration

# System VLSI Design Example Using C-Based Behavioral Synthesis

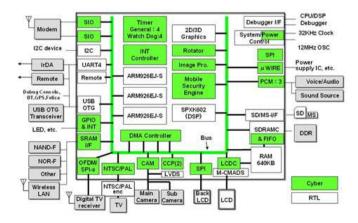

Fig.1-6 shows a design example of a real complex SoC used by a cell phones generated with the behavioral synthesizer. This SoC is called MP211, which has three ARM cores, one DSP, several dedicated hardware engines and various applications of mobile phone such as audio and video processing, voice recognition, encryption, Java and so on.

Wide ranges of circuits including control dominated circuits and data-intensive circuits were successfully implemented. The grey boxes (including bus) indicate modules that have been synthesized from C descriptions with the proposed behavioral synthesizer, while the white boxes are IP cores given in RTL format (some are legacy RTL components. All newly developed modules are designed with our C-based design flow. This example clearly illustrates that our C-based environment is able to design entire SoC designs, and not only algorithmic modules.

Figure 1-6. Behavioral design flow design example used in a cell phone SoC (Green boxes design using Cyber)

# Summary and Conclusion

The advantages of CyberWorkBench includes faster development time, hardware-software cosimulation and development, easier and faster verification as well as automatic system exploration are some of these.

CWB tool is as mature as logic synthesis in the late 80's, when designers started to use them widely RTL level design flows. These days' designers adopt this new design paradigm shifting from RTL "structural" domain thinking to "behavioral" domain thinking.

# Detailed Specification of CWB

# Behavioral Synthesis

Automatic conversion of C based code to HDL (Hardware Description Language)

Figure 2-1. Block diagram of CyberWorkBench

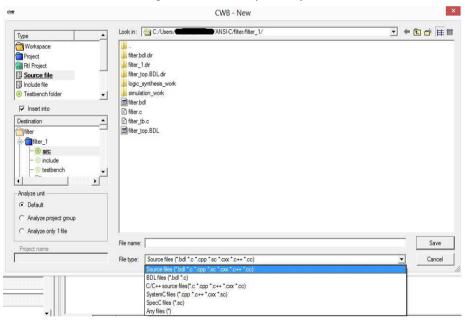

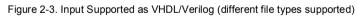

# Input supported

- a. ANSI-C

- b. System C/ SpecC

- c. VHDL (Legacy RTL with C-based design)

- d. Verilog (Legacy RTL with C-based design)

| General Key Editor                    | Menu Display Analysis/Synthesis Simulation Tool path |

|---------------------------------------|------------------------------------------------------|

| 1 1 1                                 |                                                      |

| - Analysis                            |                                                      |

| .cpp files                            | C (scpars) C Analyze as BDL (bdlpars)                |

| 1911                                  |                                                      |

| .sc files                             | C (scpars) C Analyze as SpecC (SpecC2BDL)            |

| · Analyze as System                   | c (schais) ( Milalyze as Specc (specczbbc)           |

| - Synthesis                           |                                                      |

| Update infomation file of s           | sub module if changed                                |

| C Update always                       |                                                      |

| <ul> <li>Ask me every time</li> </ul> |                                                      |

|                                       |                                                      |

| C Never update                        |                                                      |

| History of Synthesis                  |                                                      |

| Save synthesis results                | s(IFF files)                                         |

| Save synthesis enviror                | ment for each surtherin                              |

| Je Save synthesis environ             | The it for each synthesis                            |

| -User define synthesis optio          | an file                                              |

Figure 2-2. Different ways of analysis

| 3                                                        | rtlpars       | ×         |

|----------------------------------------------------------|---------------|-----------|

| C/Program Files (x86)/cyber/5.55                         | Add -> Remove |           |

| include<br>ibi<br>osci<br>osci-dbg<br>packages           | Library.      |           |

| Venlog file (*.v, *.venlog)                              | <u> </u>      | Options   |

| Verlog file (*.v. *.verlog)<br>VHDL file (*.vhd, *.vhdl) |               | OK Cancel |

Figure 2-4. Input Supported as VHDL/Verilog

# Output Languages

The output generated from CWB is VHDL/ Verilog.

Figure 2-5. Generated output as VHDL/Verilog

| Target                                                                 | C Simulation            |   | Logic Synthesis                    | C Desig                   | n Compiler                       |

|------------------------------------------------------------------------|-------------------------|---|------------------------------------|---------------------------|----------------------------------|

|                                                                        | C Synplify/Certify      | C | Leonardo Exemplar                  |                           |                                  |

| Multiplexer output format                                              |                         |   | default C case                     | C casex                   | C AND-OR C if-else               |

| default clause in the case statement                                   |                         |   | append if necessary                |                           | ge last item to default          |

| Value to be assigned at default clause in the car                      | se statement            |   | Undefined value X                  | C 0                       |                                  |

| Reset mode of FF with initial value                                    |                         |   | Default                            | C Async reset with set po | t C Async reset without set port |

| Output line number                                                     |                         |   | Yes                                | C No                      |                                  |

| Dutput tool options as comments                                        |                         | ſ | Yes                                | C No                      |                                  |

| Output empty lower hierarchy module                                    |                         |   | ' Yes                              | C No                      |                                  |

| FU output file                                                         |                         | ſ | Same file                          | C Anot                    | herfile (OP.v)                   |

| Create separate register clock pin synchronous with                    | h reverse phase         |   |                                    |                           |                                  |

| Add pragma about clock and reset infomation                            |                         |   |                                    |                           |                                  |

| Multiple internal memory of same type                                  |                         |   | <ul> <li>Same module</li> </ul>    | C Sep                     | parate module                    |

| Same instance module from each module                                  |                         |   |                                    |                           |                                  |

| NOT operation on clock for synchronous memory                          |                         |   | <ul> <li>current module</li> </ul> | C und                     | ler layer module                 |

| <ul> <li>Output memory model if it is synthesized as memory</li> </ul> | by logic synthesis tool |   |                                    |                           |                                  |

| <ul> <li>Output memory simulation description</li> </ul>               |                         |   |                                    |                           |                                  |

| Expand multi-bit port of memory into multiple one-bit                  |                         |   |                                    |                           |                                  |

| Specify module instance name in false path script f                    |                         |   |                                    |                           |                                  |

| Multi bit pin name format at design compiler false pa                  | ath script              |   |                                    |                           |                                  |

|                                                                        |                         |   |                                    |                           |                                  |

|                                                                        |                         |   |                                    |                           |                                  |

|                                                                        |                         |   |                                    |                           |                                  |

|                                                                        |                         |   |                                    |                           |                                  |

|                                                                        |                         |   |                                    |                           | Exec                             |

|                                                                        |                         |   |                                    |                           |                                  |

Figure 2-6(a). Different options available for selected output as Verilog

| CWB - Venlogg                                                 | gen Option - filter(/filter/filter_1) |                                        |          |

|---------------------------------------------------------------|---------------------------------------|----------------------------------------|----------|

| eneral Hierarchy Format                                       |                                       |                                        |          |

| Herarchize module                                             | 1                                     | 22                                     |          |

| Multiplexer, register<br>Hierarchize multiplexer              |                                       | <ul> <li>Do not hierarchize</li> </ul> |          |

| Expand to same hierarchy                                      |                                       |                                        |          |

| C Hierarchize and set to lower hierarchy module               |                                       |                                        |          |

| Specify hierarchy multiplexer More than 4 bits, and More than | 8 branches                            |                                        |          |

| Change top module name                                        |                                       |                                        |          |

| Top module name :                                             |                                       |                                        |          |

| Add prefix for all lower modules                              |                                       |                                        |          |

| <ul> <li>Use top module name as prefix</li> </ul>             |                                       |                                        |          |

| C Use the specified strings as prefix                         |                                       |                                        |          |

| Add process name as prefix for functional units               |                                       |                                        |          |

| Add process name as prefix for memory                         |                                       |                                        |          |

| Add process name as prefix for decoders                       |                                       |                                        |          |

| Add pragma for cyber to module definition                     |                                       |                                        |          |

|                                                               |                                       |                                        |          |

|                                                               |                                       |                                        |          |

|                                                               |                                       |                                        |          |

|                                                               |                                       |                                        |          |

|                                                               |                                       |                                        |          |

|                                                               |                                       |                                        |          |

|                                                               |                                       |                                        |          |

|                                                               |                                       |                                        |          |

|                                                               |                                       |                                        |          |

|                                                               |                                       |                                        | Execu    |

|                                                               |                                       |                                        |          |

| Default Additional Options - Load Save                        |                                       |                                        |          |

|                                                               |                                       | ·                                      |          |

|                                                               |                                       | OK Ca                                  | ancel Ap |

Figure 2-6(b). Different options available for selected output as Verilog

| neral Hierarchy Format                         |                                               |                                                                  |       |

|------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------|-------|

| Style of register 📀 d                          | lock enable style                             |                                                                  |       |

| Suffix of register name                        |                                               |                                                                  |       |

| Dump attribute 🙃 E                             | nable                                         | C Disable                                                        |       |

|                                                | stbench.INST_0 C Specify                      |                                                                  |       |

|                                                | lexadecimal C Decimal C C                     |                                                                  |       |

|                                                | nplement with simple algorithm                | <ul> <li>Output with operator code</li> </ul>                    |       |

|                                                | lse unsigned functional unit and sign conve   |                                                                  |       |

|                                                |                                               | ine synopsis Design Ware 🔿 NEC Design Ware                       |       |

| addsub type                                    | C select                                      | ( share                                                          |       |

| Pipeline functional unit(s)                    |                                               | nodel C Simulation model only for unsupported functional unit(s) |       |

| FSM state number                               | <ul> <li>Parameter variable (with:</li> </ul> |                                                                  |       |

|                                                | Parameter variable (with                      |                                                                  |       |

| Assignment code with combinational circuit alv |                                               | C a<=b                                                           |       |

| Assignment code within LATCH circuit always    |                                               | (• a<=b                                                          |       |

| Insert absolute delay to register substitution | OFF                                           | CON                                                              |       |

| Parameter name                                 |                                               |                                                                  |       |

| Delay value                                    | 1                                             |                                                                  |       |

| 'define identifier                             |                                               |                                                                  |       |

| "define file name                              |                                               | Browse                                                           |       |

| Generate 'define file                          | C OFF                                         | CON                                                              |       |

| Insert delay to async reset                    | C OFF                                         | CON                                                              |       |

| Decoder output format                          | Index format                                  | C for loop format C case format                                  |       |

| ** **                                          | 18.95 J. 1.                                   |                                                                  |       |

|                                                |                                               |                                                                  | _     |

|                                                |                                               |                                                                  | Execu |

|                                                |                                               |                                                                  |       |

Figure 2-6(c). Different options available for selected output as Verilog

### Target Device Supported

Full ASIC/ FPGA support

Support all FPGA families from Xilinx and Altera

The Generated RTL is optimized for the specified technology.

| 1.Basic Settings<br>Clock period        | 1000 1/100ns 💌 =               | 10 ns (Frequency: 100 MHz ) |               |

|-----------------------------------------|--------------------------------|-----------------------------|---------------|

| Clock uncertainty                       | 200.00 ( 1/100ns ) =           | 2ns                         |               |

| C Absolute valu                         | e of delay ( 1/100ns           | )  Percentage of the clo    | ck period     |

| Effective clock period                  | i 800.00 (1/100ns) =           | 9 co                        |               |

|                                         |                                | 0115                        |               |

| Library                                 | ry C Select Existing Library   |                             |               |

| -2 Device                               | y v Sciect Existing Ebility    |                             |               |

| FPGA                                    | C ASIC                         |                             |               |

| family name                             | cycloneV 💌                     |                             |               |

| device name                             | virtex 🔺                       |                             |               |

| package name                            | virtex2                        |                             |               |

| - 10 - 10 - 10 - 10 - 10 - 10 - 10 - 10 | virtex2p                       |                             |               |

| speed grade                             | virtex4                        |                             |               |

|                                         | virtex5                        |                             |               |

| Logic synthesis tool                    | virtex6                        | Follow the logic synthesi   | is tool in ba |

|                                         | virtex6-lower-power<br>virtex7 |                             |               |

| 3.Basic Library                         | virtexu                        |                             |               |

| 1                                       | zyng                           |                             |               |

| Setting                                 | Stop                           |                             |               |

| \${CYBER_PATH}/                         | packages/fpga_cv.BLIB          |                             |               |

| Delete                                  |                                |                             |               |

| Delete                                  |                                |                             |               |

|                                         | al Unit Library                |                             |               |

| -4.Standard Function                    |                                |                             |               |

| -4.Standard Function<br>Setting         | Stop                           |                             |               |

| Setting                                 |                                |                             |               |

| Setting                                 | Stop<br>packages/fpga_cv.FLIB  |                             |               |

| Setting                                 |                                |                             |               |

| Setting                                 |                                |                             |               |

| Setting                                 |                                | T                           | Modify        |

Figure 2-7. Different options for selecting families of Xilinx and Altera

#### Input Constraints

Ability to specify the clock frequency

Ability to specify reset signal and its type.

Ability to control resource allocation: CWB allow user to specify any resource constraints that is desired during implementation of the specific module.

| ibrary type GE                            | NERATED                                                              |        |           |                                              |                 | Library name   | ilter           |           |            |               |         |          |

|-------------------------------------------|----------------------------------------------------------------------|--------|-----------|----------------------------------------------|-----------------|----------------|-----------------|-----------|------------|---------------|---------|----------|

| Library file for an                       | thmetic operat                                                       | ors    |           |                                              | •               | Unit 1/10      | ▼ ps ▼          |           |            |               |         |          |

| ibrary file for ba<br>Ibrary file for art | Inmetic operati                                                      | 018    |           |                                              |                 |                |                 |           |            |               |         |          |

| FPGA Settings<br>Family cyclor            |                                                                      |        | Device    |                                              |                 | Package        | [               |           | Speed      | 1             |         |          |

| unction unit                              | Add                                                                  | Delete | Copy      |                                              |                 |                |                 |           |            |               |         |          |

| Operator name                             | Kind                                                                 | Sign   | Bit width | Delay                                        | Delay(Input-Rej | Delay(Reg-Out; | Area(Combinatio | Area(REG) | MACRO_BLOC | DSP implement | NETLIST | NET      |

|                                           |                                                                      | 1      | *         |                                              |                 |                |                 |           |            | •             | 2       | -        |

| c]                                        |                                                                      |        |           |                                              |                 |                |                 |           |            |               |         |          |

| C +<br>Kind C Funct                       | ion operator n                                                       | ame    | < >> < >> |                                              | **              |                |                 |           |            |               |         |          |

| Kind C Funct<br>C Arithm<br>C Arithm      |                                                                      | ame    | St        |                                              | Unit 1/"        |                |                 |           |            |               |         | <u>1</u> |

| Kind C Funct<br>C Anthro<br>C Al<br>C Sp  | netic operator i<br>osolute delay<br>pecify cycle<br>pecify pipeline | ame    | St        | Cycle (A sma<br>age count<br>slay(Input-Reg) | Unit 1/"        |                |                 |           |            |               |         | <u>1</u> |

Figure 2-8. Function unit libraries for input constraints

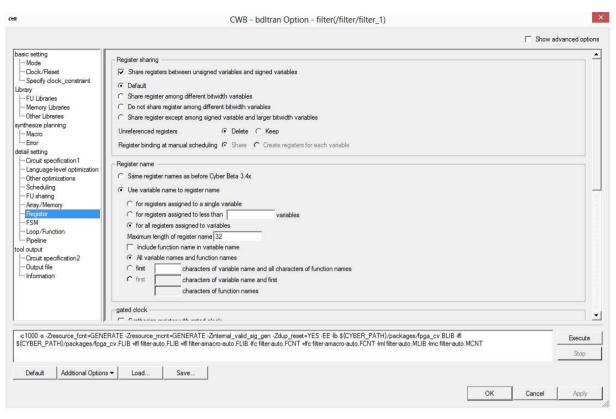

| e.                                                             | CV                                                    | VB - bdltran Option - filter(     | filter/filter_1)       |                           |             |              |      |

|----------------------------------------------------------------|-------------------------------------------------------|-----------------------------------|------------------------|---------------------------|-------------|--------------|------|

|                                                                |                                                       |                                   |                        |                           | ☐ Show      | v advanced o | ptio |

| asic setting<br>Mode<br>Clock/Reset                            | -Macro options                                        |                                   |                        |                           |             |              |      |

| Specify clock_constraint                                       | Priority for execution time                           |                                   |                        |                           |             |              |      |

| brary                                                          | 1                                                     | 1                                 |                        |                           |             |              |      |

| FU Libraries                                                   | NO 1                                                  | 2                                 | 3                      | 4                         |             | 5            |      |

| Memory Libraries                                               | Optimize                                              |                                   |                        | Not optimize              |             |              |      |

| Other Libraries                                                | Long synthesis time                                   | <>                                |                        | Short synthesis time      |             |              |      |

| nthesize planning                                              | Other option have priority over Macro                 |                                   |                        | Short aynu load tine      | -           |              |      |

| Macro                                                          | Contra option nave privily over made                  |                                   |                        |                           |             |              |      |

| Error                                                          | Priority for circuit area                             |                                   |                        |                           |             |              |      |

| stail setting                                                  |                                                       |                                   |                        |                           |             |              |      |

| Circuit specification1                                         | 1                                                     |                                   |                        |                           |             |              |      |

| Language-level optimization                                    | NO 1                                                  | 2                                 | 3                      | 4                         |             | 5            |      |

| • Other optimizations                                          | Large area                                            |                                   |                        | Small area                |             |              |      |

| Scheduling                                                     | Fast execution                                        | ç                                 |                        | Slow execution            |             |              |      |

| FU sharing                                                     | Other option have priority over Macro                 |                                   |                        |                           | -           |              |      |

| - Array/Memory                                                 |                                                       |                                   |                        |                           | -           |              |      |

| Register<br>FSM                                                | Priority for cycle                                    |                                   | Priority for delay     |                           |             |              |      |

| ··· Loop/Function                                              |                                                       |                                   |                        |                           |             |              |      |

| - Pipeline                                                     | 1. C. 1.                                              | 2 3                               |                        | 1 2                       |             | 3            |      |

| ol output                                                      | NO 1                                                  |                                   | NO                     | 1 4                       |             | 3            |      |

| ·· Circuit specification2                                      | Short cycle                                           | Long cycle                        | Large delay            | <>                        | Small delay |              |      |

| - Output file                                                  | Large area                                            | Small area                        | Small area             |                           | Large area  |              |      |

| - Information                                                  | Other option have priority over Macro                 | •                                 | Other option have pri  | ionty over Macro          |             | -            |      |

|                                                                | - Other Options                                       |                                   |                        |                           |             |              |      |

|                                                                |                                                       |                                   |                        |                           |             | -            |      |

| MA1 -c1000 -s -Zresource_font=0<br>[CYBER_PATH]/packages/fpga_ | SENERATE -Zresource_mont=GENERATE -Zinter<br>_cv.FLIB | nal_valid_sig_gen -Zdup_reset=YES | EE Ib \$(CYBER_PATH)/p | ackages/fpga_cv.BLIB -ffl |             | Execu        | ,t   |

|                                                                |                                                       |                                   |                        |                           |             | Stop         | p    |

| Default Additional Options                                     | ▼ Load Save                                           |                                   |                        |                           |             |              |      |

|                                                                |                                                       |                                   |                        | ОК                        | Cancel      | 1            |      |

|                                                                |                                                       |                                   |                        | UK                        | Cancel      | Арр          | iy   |

Figure 2-9. Different options for synthesize planning to control resource allocation.

| -                | Add           | Delete                            |       | бору           |      |                  |                 |                      |                     |

|------------------|---------------|-----------------------------------|-------|----------------|------|------------------|-----------------|----------------------|---------------------|

| Operator name    | Max. FU count | Max. FU count<br>for folding loop | Alias | Kind           | Sign | Bit width        | Delay           | Delay<br>(Input-Reg) | Delay<br>(Reg-Outpu |

|                  |               |                                   |       |                |      |                  |                 |                      |                     |

|                  |               |                                   |       |                |      |                  |                 |                      |                     |

|                  |               |                                   |       |                |      |                  |                 |                      |                     |

|                  |               |                                   |       |                |      |                  |                 |                      |                     |

|                  |               |                                   |       |                |      |                  |                 |                      |                     |

| 4                |               |                                   |       |                |      |                  |                 |                      | <u>,</u>            |

| Maximum FU       | count + -     | 1                                 | For   | folding loop . |      | 1                |                 |                      |                     |

|                  |               | J                                 |       |                |      |                  |                 |                      |                     |

|                  | ect Add       | Delete                            |       |                |      |                  |                 |                      |                     |

| Specify chain ef | ea Aub        |                                   |       | Operator name  |      | Specify chain de | stination delay |                      |                     |

| Specify chain ef |               | Chain destination                 |       | porotor manie  |      | -                |                 |                      |                     |

|                  |               | Chain destination                 | (     | poracol marine |      |                  |                 |                      |                     |

|                  |               | Chain destination                 |       | perecer menne  |      |                  |                 |                      |                     |

Figure 2-10. Different options for function constraint to control resource allocation.

| Main Analysis                     | Error Display                                |

|-----------------------------------|----------------------------------------------|

| -1.Basic Settings<br>Clock period | 1000 1/100ns 💌 = 10 ns (Frequency: 100 MHz ) |

| Clock uncertainty                 | 200.00 ( 1/100ns ) = 2ns                     |

Figure 2-11. Options for specifying clock frequency

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Show advanced op |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| basic setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Clock/Reset port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |

| "Mode     "Glock/Rest     "Glock/Rest     "Glock/Rest     "Glock/Rest     "FU Ubraites     "FU Ubraites     "Memory Libraries     "Other Ubraites     "Other Ubraites     "The Ubraites | Cubch Needs point Clock Name CLOCK  Reining edge C Falling edge When not specified C Do not create when not required C Create always G Generate clock signal dedicated for inversed edge triggered registers Clock signal name C Clock name + "_FRUV" C Specify Reset Name RESET C Active high C Active low C Synchronous C Asynchronously The number of registers inserted at reset input F Make a duplicate of reset signal in each clock domain When not specified C D on to create when not required C Create always |                  |

| Circuit specification2     Output file     Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Initial values at variable declaration C Assign at the reset state C Assign at the first state                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |

| and the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Reset state creation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  |

| -c1000 -s -Zresource_fcnt=GENE<br>\${CYBER_PATH}/packages/fpga                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Execut<br>Stop   |

Figure 2-12. Settings for frequency reset

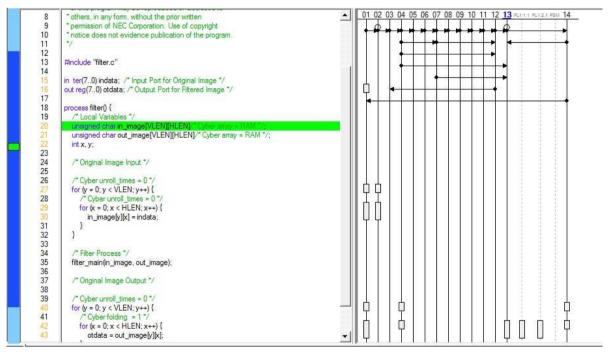

# Behavioral Synthesis modes or Scheduling options (C to RTL conversion modes)

- Automatic scheduling

- Manual Scheduling

- Mixed Scheduling (user specific)